Laboratory Coordinator: Dr. Jack Ou - (818) 677-2190 - jack.ou@csun.edu

Overview:

California State University, Northridge is a CADENCE University Program Member.

Cadence Design Systems has the most comprehensive software toolsets for any type of digital IC implementation. Cadence provides end-to-end solutions for nearly any type of electronic design. Its proven products have helped companies around the world to design everything from the largest electronic systems to leading-edge mixed-signal SoCs.

Cadence tools are organized into a number of featured applications. Each contains the complete set of tools, regardless of the design technology needed to address that particular application. Cadence tools are also organized into the following nine standard design technologies:

- System-level Design

- Functional Verification

- Emulation and acceleration

- Synthesis/Place-and-Route

- Analog, RF, and Mixed-Signal Design

- Custom IC Layout

- Physical Verification and Analysis

- IC Packaging

- PCB Design

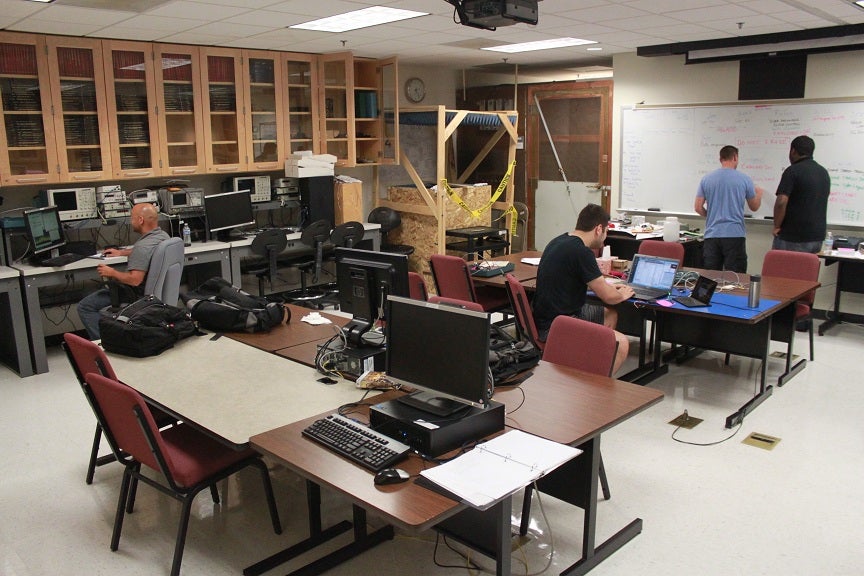

Most of these tools are available for our students in both the ASIC Design Laboratory (JD1102) and the Senior Design Laboratory (JD2201). Additionally, Cadence mixed signal simulation tools are used in research laboratories for physical synthesis.

The Senior Design Laboratory is utilized by our senior students in designing, developing and building their senior projects. Cadence circuit board layout programs are among the tools used there.

Applications in Class:

Cadence product simulators serve both ECE 340/L and 440/L in the JD 1566 lab. In ECE 340/L, we measure diode and bipolar transistor parameters for use in breakout models. We also measure parameters for use in MOSFET breakout models. Simulations are compared to bench measurements for student-designed circuits.

In ECE 440/L, the main focus is on accurate measurements to precisely predict the performance of amplifiers using breakout models. Student-designed amplifiers are compared to simulations over voltage, time and frequency.

Cadence SPICE simulators serve ECE 320/L in the JD 1601 lab where we use discrete digital circuits from the 4000 and 7400 series. Students compare bench performance to simulated timing diagrams up for several variables.

Cadence product simulators also serve ECE 442/L, 443/L and 425/L in the JD 1607 lab. In 442/L, the main focus is on accurate measurements for MOS transistors to accurately predict the performance of digital circuits ranging from inverters to 8 bit counters. Breakout models are used extensively. CMOS technology is emphasized.

In ECE 443/L, the main focus is on breakout models for MOSFETs to accurately predict the performance of comparator, digital to analog, and analog to digital circuits. Breakout models are used extensively. Student-designed digital circuits are compared to simulation values for voltage, and timing.

The Application Specific Integrated Circuit (ASIC) lab is located in Jacaranda Hall (JD 1102). In the lab, are 30 HP Linux/Windows workstations that can accommodate 30 students and a laser printer. It supports ECE 526L (Verilog and SystemVerilog for Digital Integrated Circuit Design Lab), ECE 527L (Application Specific Integrated Circuit Development Lab), ECE 640 (Modern Electronic Techniques), ECE 642 (RF Electronics Design), ECE 648 (Electrical Network Theory) and ECE 649 (Active Network Synthesis). Cadence packages such as Virtuoso Design Environment (IC 6.17) and Physical Verification System (PVS 152) are installed on these machines in order to support design, simulation and physical implementation of integrated circuits.

Digital simulators from Cadence and Synopsys are running on these machines as well as a full suite of backend tools for synthesis, layout and timing analysis.

*Cadence is a registered trademark of Cadence Design Systems, Inc., 2655 Seely Avenue, San Jose, CA 95134.

(Last Updated: 08/04/2017)